Материалы по тегу: pci express 6.0

|

01.05.2024 [17:00], Сергей Карасёв

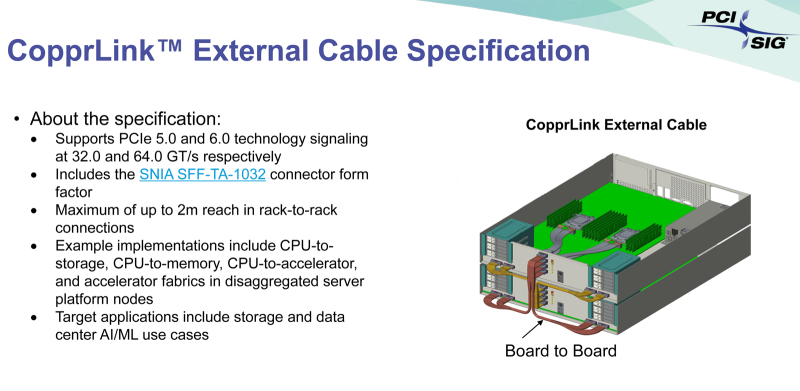

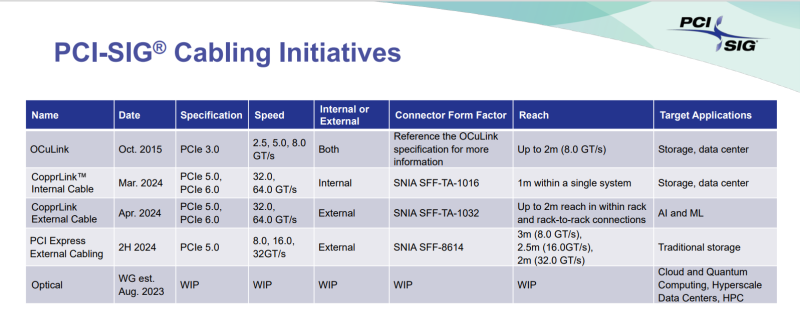

Внутри и снаружи: PCI-SIG обнародовала спецификации кабелей CopprLink для PCIe 5.0/6.0Организация PCI Special Interest Group (PCI-SIG) обнародовала спецификации электрических кабелей и разъёмов CopprLink для внешних и внутренних подключений PCIe 5.0/6.0. Новые соединения на основе меди позволят заменить существующие кабели OCuLink в тех случаях, когда требуется более высокая пропускная способность. Стандарт CopprLink был анонсирован в конце 2023 года. Кабели данного типа обеспечат высокоскоростные подключения в пределах отдельных систем, а также между различными узлами в составе стойки. Кроме того, как отмечалось ранее, разрабатываются варианты для межстоечного соединения. Спецификация CopprLink для внутренних подключений:

Спецификация CopprLink для внешних подключений:

Отмечается, что в дальнейшем кабели CopprLink будут развиваться с учётом возможностей интерфейса PCIe следующих поколений. Технология CopprLink, как ожидается, будет востребована в сферах, где необходимы небольшие задержки, включая дата-центры, производительные СХД, сети и пр. В будущем ожидается появление оптических кабелей PCIe.

14.03.2024 [23:45], Алексей Степин

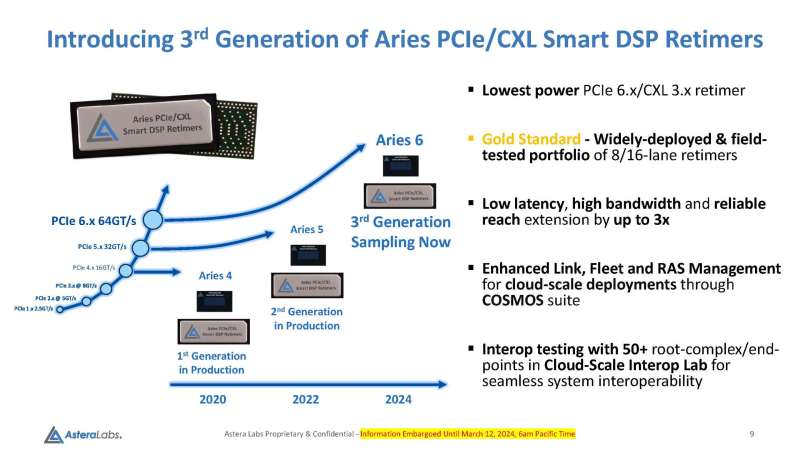

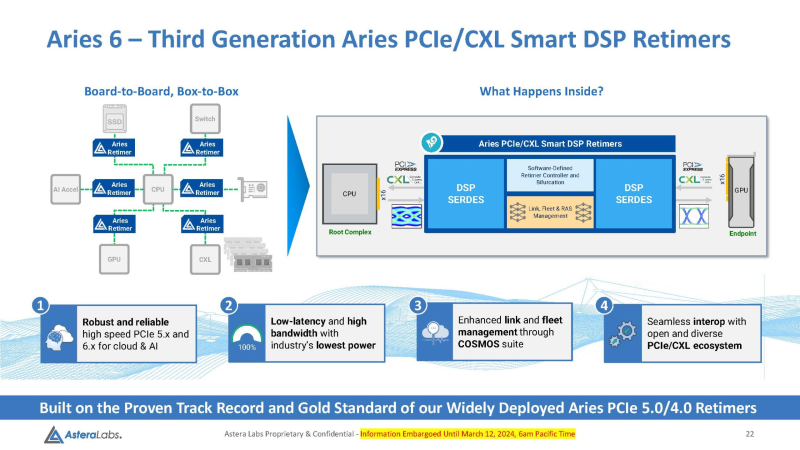

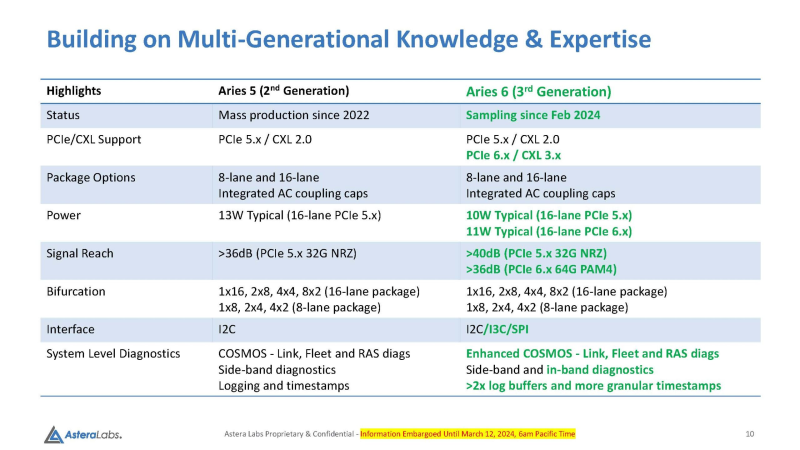

Войны ретаймеров: Astera Labs анонсировала чипы Aries 6 для PCIe 6.0Практически сразу после анонса чипов Broadcom Vantage 5 и 6 Astera представила свой вариант ретаймеров для инфраструктуры PCIe следующего поколения — серию чипов Aries 6, передаёт ServeTheHome. Высокий интерес к ретаймерам вызван теми возможностями, что открывает PCI Express 6.0 как в плане скоростей, так и в плане функциональности (CXL). А переход на новое поколение шины необходим для дальнейшего развития набирающего популярность генеративного ИИ. По мере роста скоростей PCI Express обострялась и проблема длины проводников на печатной плате, при которой сигнал достаточно устойчив и вписывается в окно требуемых характеристик. Если при переходе от PCIe 3.0 к 4.0 удалось обойтись сравнительно малой кровью, то для PCIe 5.0 уже потребовались более сложная схемотехника и более продвинутые ретаймеры. PCIe 6.0 же накладывает ещё более жёсткие требования к целостности сигнала. Платформы GPU-кластеров и СХД компактнее не становятся, так что требуемая длина проводников на печатных платах растёт, а вместе с ней растёт и важность ретаймеров, поскольку без них согласовать высокоскоростной сигнал PCIe 6.0 становится невозможно. Таким системам требуется сразу несколько подобных чипов, причём стоимость каждого из них достигает $20, так что суммарная стоимость этих компонентов на уровне целого ЦОД весьма внушительна. Новые чипы Aries 6 относятся к третьему поколению «умных» DSP-ретаймеров. Они представлены в вариантах с 8 и 16 линиями PCIe 6.0 и позволяют в три раза увеличить длину соответствующего соединения на плате, говорит Astera Labs. При этом новинки поддерживают CXL 3.x и предоставляют расширенные средства диагностики и управления COSMOS. Энергопотребление в режиме PCIe 6.0 при этом заявлено меньше, чем у Broadcom Vantage 6 — 11 Вт против 13 Вт у конкурента. Aries 6 уже протестированы на совместимость с полсотней разнообразных PCIe-соединений, включая root-комплексы и конечные устройства. И если Broadcom пока только говорит о ретаймерах для PCIe 6.0, а появление первого «кремния» Vantage 6 запланировано лишь на следующий год, то Astera Labs начала поставки образцов Aries 6 ещё в феврале. Похоже, Broadcom будет нелегко развернуться на этом рынке.

08.03.2024 [00:03], Алексей Степин

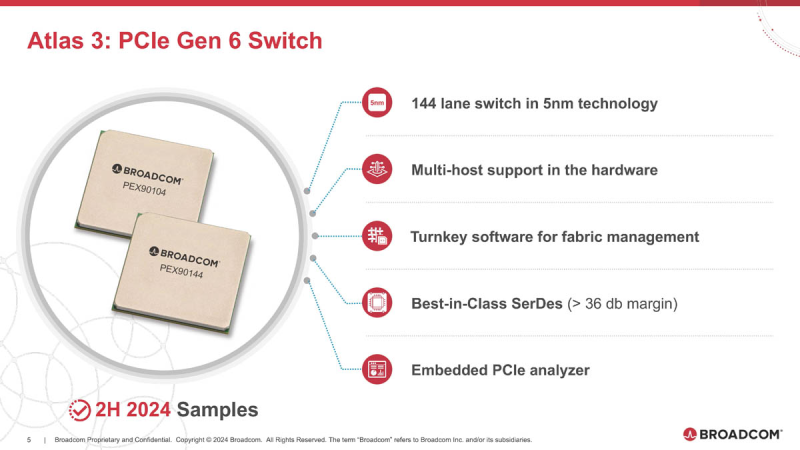

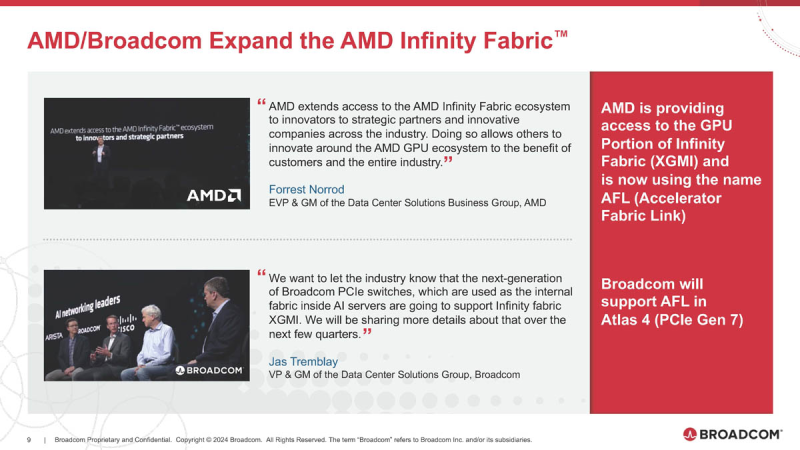

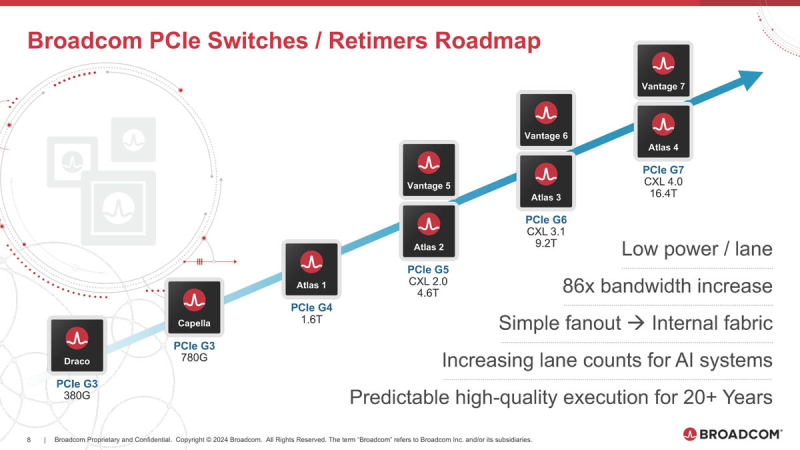

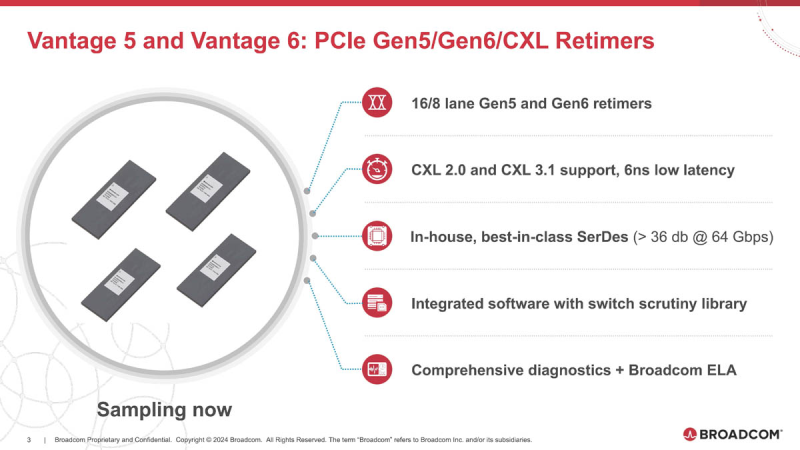

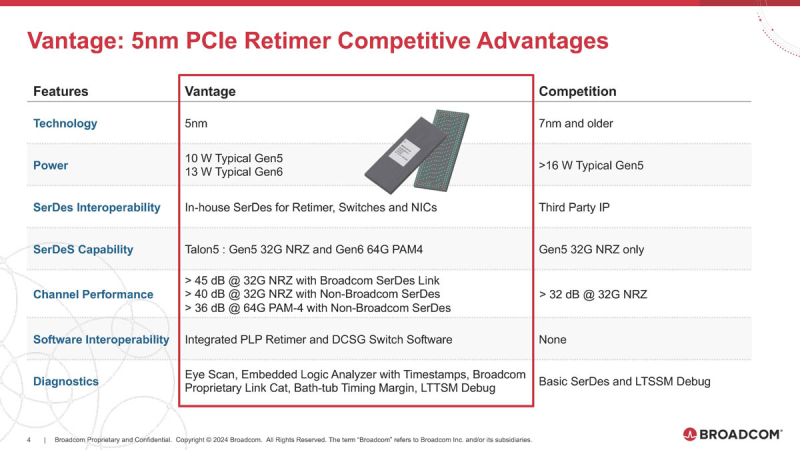

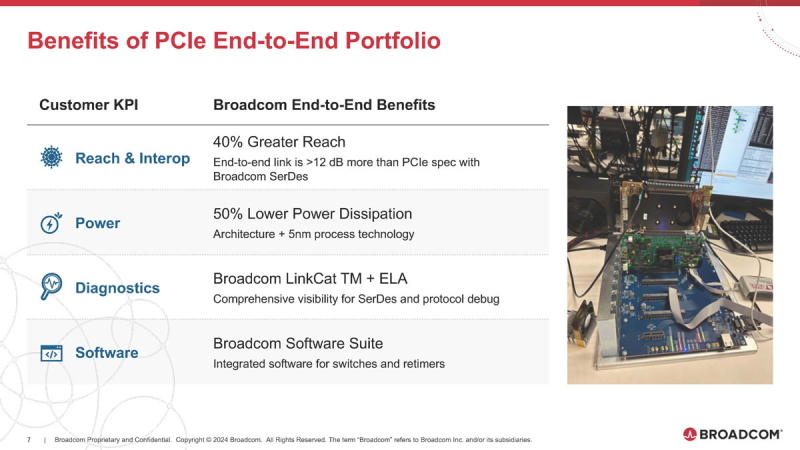

Broadcom готовит чипы для PCIe 6.0/7.0 с поддержкой AMD Infinity FabricОдним из столпов, на которых зиждется господство NVIDIA в мире ускорителей, является NVLink — высокоскоростной интерконнект, позволяющий чипам общаться напрямую не только в составе одного узла, но и за его пределами. AMD пытается ответить на это продвижением XGMI/Infinity Fabric, и в предварительном обзоре Instinct MI300 были затронуты вопросы топологии серверов в исполнении «красных». Ещё тогда, в момент анонса MI300, компания Broadcom объявила о поддержке данного интерконнекта в будущих поколениях своих PCIe-коммутаторов, а сейчас ресурс ServeTheHome поделился новыми подробностями. XGMI действительно станет коммутируемым, что упростит масштабирование систем на базе ускорителей AMD Instinct. Интерконнект получил официально название AFL (Accelerated Fabric Link). В основе AFL по-прежнему будет лежать PCI Express, в данном случае речь идёт уже о PCI Express 7.0. Поддержка данной технологии дебютирует в PCIe-коммутаторах Broadcom Atlas 4. В дополнение к ним будут выпущены и новые ретаймеры Vantage 7, которые также получат поддержку CXL 4.0. Но перед этим Broadcom начнёт поставки образцов чипов-коммутаторов Atlas 3 со 144 линиями PCIe 6.0 во II половине 2024 года, а серверы с такими коммутаторами появятся в 2025 году. Поддержка CXL здесь будет расширена до версии 3.1. Что касается ретаймеров, то здесь Broadcom уже нанесла ответный удар Astera Labs, анонсировав чипы серий Vantage 5 и Vantage 6 для экосистем PCI Express 5.0 и PCI Express 6.0 соответственно. Они будут выпускаться в вариантах с 8 и 16 линиями с опцией бифуркации и поддержкой CXL 2.0 и 3.1. Broadcom заявляет о более низком энергопотреблении, достигнутом за счёт применения 5-нм техпроцесса, лучших в индустрии блоках SerDes и расширенных средствах диагностики, интегрированных в новые ретаймеры. Экономичность здесь играет важную роль: хотя даже 7-нм ретаймер потребляет немного, таких микросхем в составе каждого GPU-сервера несколько, что при дальнейшем масштабировании выливается весьма серьёзные цифры. К тому же меньшая нагрузка ляжет и на систему охлаждения, ведь если CPU и ускорители могут обслуживаться СЖО, то остальные компоненты в таких серверах по-прежнему охлаждаются обычными вентиляторами. Что касается SerDes-блоков, то они позволят на 40 % удлинить соединения при сохранении стабильной работы. Ну а наличие продвинутого диагностического программного обеспечения с расширенными возможностями упростит разработку, отладку и ремонт систем нового поколения. Ретаймеры Vantage 5 будут использоваться в комплекте с коммутаторами Atlas 2 в решениях Broadcom уже сегодня, они обеспечат поддержку CXL 2.0, ну а системы с Vantage 6 и поддержкой CXL 3.1, как уже упоминалось, должны увидеть свет в следующем году. Astera Labs есть о чём беспокоиться: если на данный момент её ретаймерам почти нет альтернативы, то уже в ближайшем будущем ситуация может коренным образом измениться, поскольку Broadcom явно осознала всю важность этого компонента в экосистеме PCI Express и оценила солидный объём потенциальной клиентской базы.

02.08.2022 [16:00], Алексей Степин

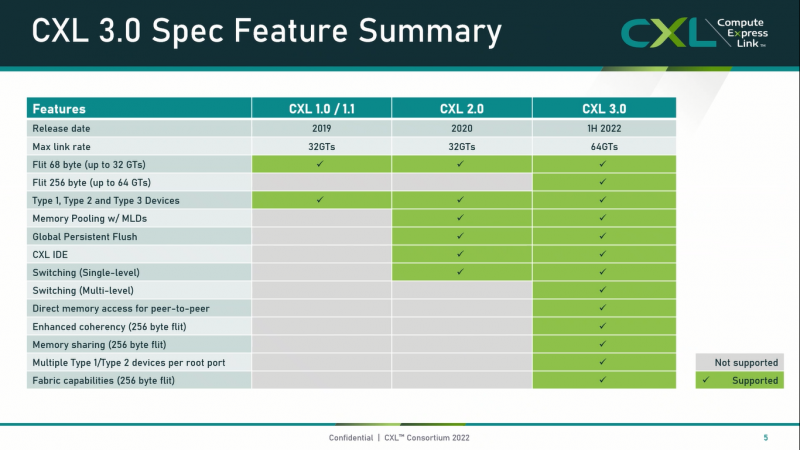

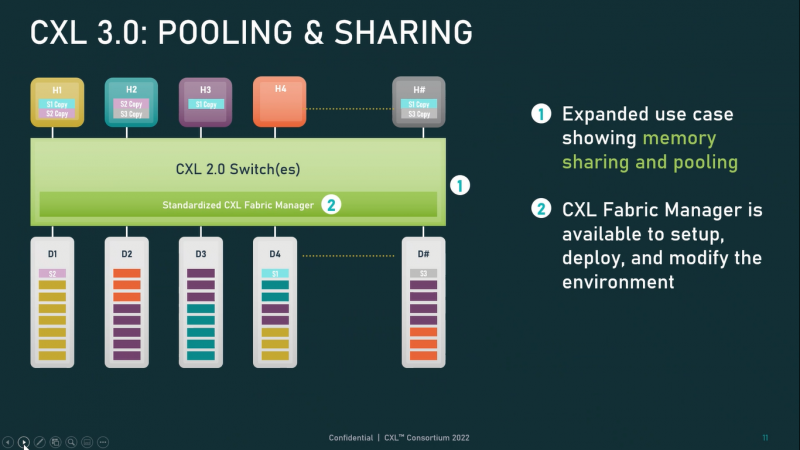

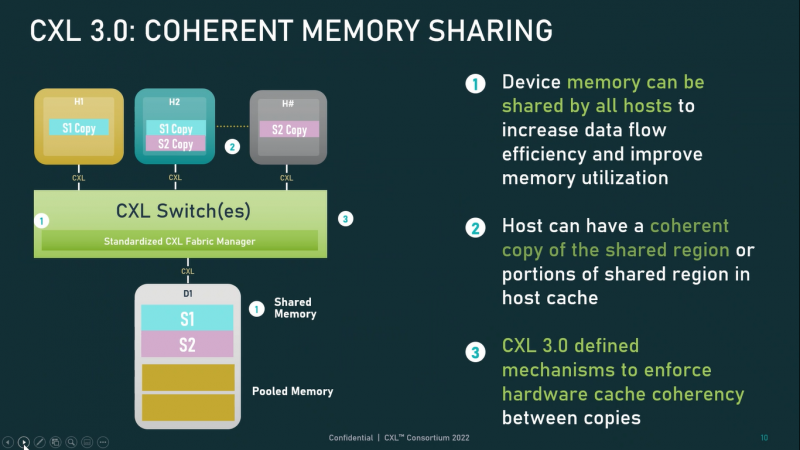

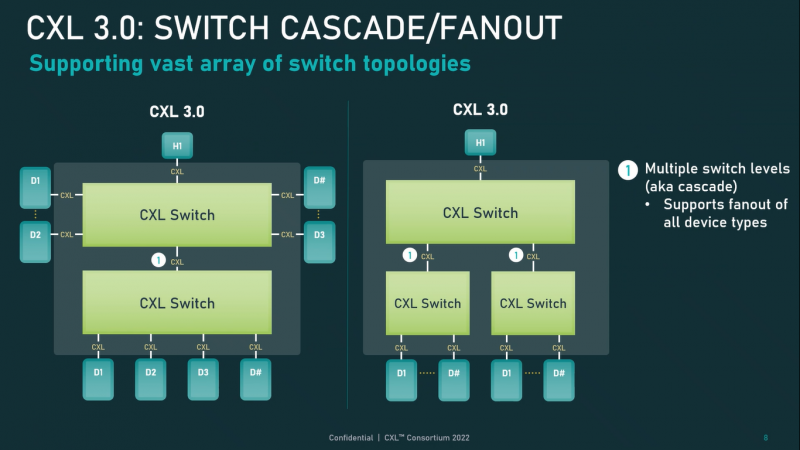

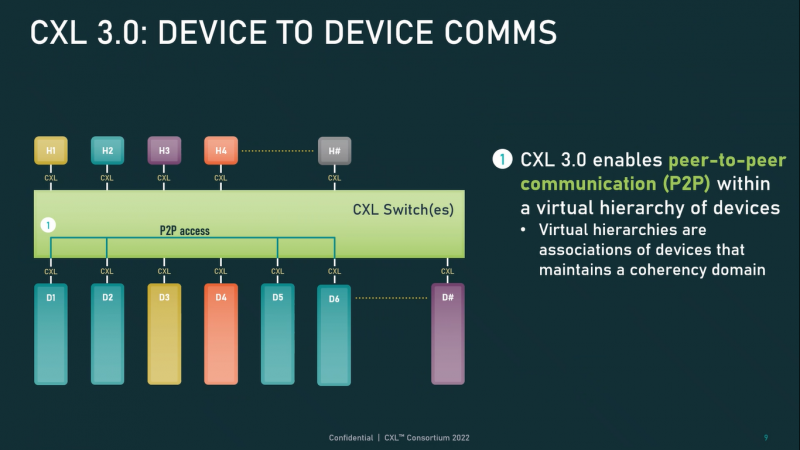

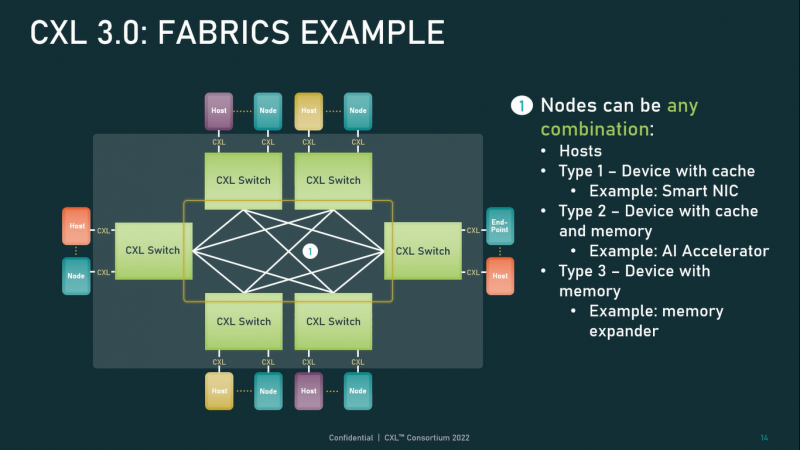

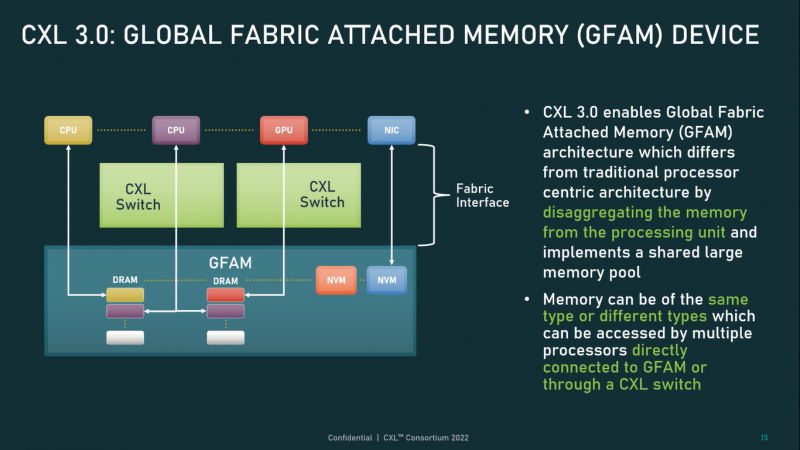

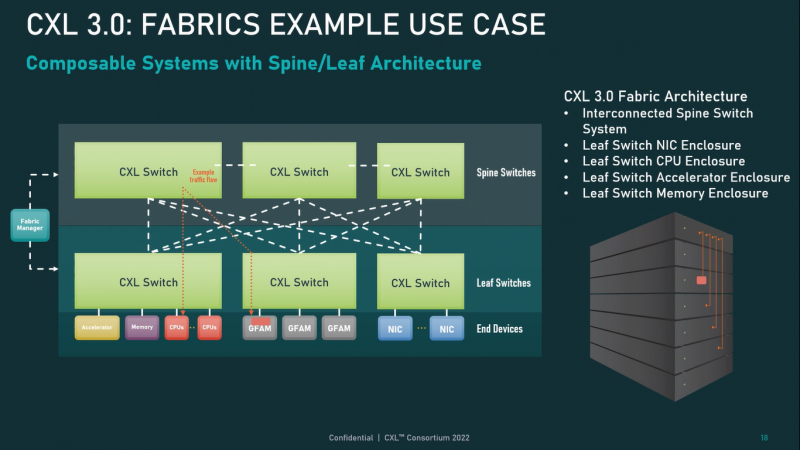

Опубликованы спецификации Compute Express Link 3.0Мало-помалу стандарт Compute Express Link пробивает себе путь на рынок: хотя процессоров с поддержкой ещё нет, многие из элементов инфраструктуры для нового интерконнекта и базирующихся на нём концепций уже готово — в частности, регулярно демонстрируются новые контроллеры и модули памяти. Но развивается и сам стандарт. В версии 1.1, спецификации на которую были опубликованы ещё в 2019 году, были только заложены основы. Но уже в версии 2.0 CXL получил массу нововведений, позволяющих говорить не просто о новой шине, но о целой концепции и смене подхода к архитектуре серверов. А сейчас консорциум, ответственный за разработку стандарта, опубликовал свежие спецификации версии 3.0, ещё более расширяющие возможности CXL. И не только расширяющие: в версии 3.0 новый стандарт получил поддержку скорости 64 ГТ/с, при этом без повышения задержки. Что неудивительно, поскольку в основе лежит стандарт PCIe 6.0. Но основные усилия разработчиков были сконцентрированы на дальнейшем развитии идей дезагрегации ресурсов и создания компонуемой инфраструктуры. Сама фабрика CXL 3.0 теперь допускает создание и подключение «многоголовых» (multi-headed) устройств, расширены возможности по управлению фабрикой, улучшена поддержка пулов памяти, введены продвинутые режимы когерентности, а также появилась поддержка многоуровневой коммутации. При этом CXL 3.0 сохранил обратную совместимость со всеми предыдущими версиями — 2.0, 1.1 и даже 1.0. В этом случае часть имеющихся функций попросту не будет активирована. Одно из ключевых новшеств — многоуровневая коммутация. Теперь топология фабрики CXL 3.0 может быть практически любой, от линейной до каскадной с группами коммутаторов, подключенных к коммутаторам более высокого уровня. При этом каждый корневой порт процессора поддерживает одновременное подключение через коммутатор устройств различных типов в любой комбинации. Ещё одним интересным нововведением стала поддержка прямого доступа к памяти типа peer-to-peer (P2P). Проще говоря, несколько ускорителей, расположенных, к примеру, в соседних стойках, смогут напрямую общаться друг с другом, не затрагивая хост-процессоры. Во всех случаях обеспечивается защита доступа и безопасность коммуникаций. Кроме того, есть возможность разделить память каждого устройства на 16 независимых сегментов. При этом поддерживается иерархическая организация групп, внутри которых обеспечивается когерентность содержимого памяти и кешей (предусмотрена инвалидация). Теперь помимо эксклюзивного доступа к памяти из пула доступен и общий доступ сразу нескольких хостов к одному блоку памяти, причём с аппаратной поддержкой когерентности. Организация пулов теперь не отдаётся на откуп стороннему ПО, а осуществляется посредством стандартизированного менеджера фабрики. Сочетание новых возможностей выводит идею разделения памяти и вычислительных ресурсов на новый уровень: теперь возможно построение систем, где единый пул подключенной к фабрике CXL 3.0 памяти (Global Fabric Attached Memory, GFAM) действительно существует отдельно от вычислительных модулей. При этом возможность адресовать до 4096 точек подключения скорее упрётся в физические лимиты фабрики. Пул может содержать разные типы памяти — DRAM, NAND, SCM — и подключаться к вычислительным мощностями как напрямую, так и через коммутаторы CXL. Предусмотрен механизм сообщения самими устройствами об их типе, возможностях и прочих характеристиках. Подобная архитектура обещает стать востребованной в мире машинного обучения, в котором наборы данных для нейросетей нового поколения достигают уже поистине гигантских размеров. В настоящее время группа CXL уже включает 206 участников, в число которых входят компании Intel, Arm, AMD, IBM, NVIDIA, Huawei, крупные облачные провайдеры, включая Microsoft, Alibaba Group, Google и Meta✴, а также ряд крупных производителей серверного оборудования, в том числе, HPE и Dell EMC. |

|